STM32F7 RCC(リセットとクロック)

- 2020.08.10

- STM32F7

引き続きSTM32F7の機能について記述していく。今回はリセットとクロックについて。以下にマニュアルと書かれているのはリファレンスマニュアル(RM0410 Rev4)のことを指している。

リセット

STM32F7には3種類のリセットがある。RCC_CSRレジスタの31~25ビット目を見れば発生したリセット要因が分かる。これらのビットは同じくRCC_CSRのRMVFビットをクリアすることで全てクリアされる。ちなみにこのRMVFビットだが、マニュアルにはrw(読み書き可能)と書かれているが、実際に動かして確認した感じだとrc_w1(読み込みのみ可能、1を書き込むとクリア)に思える。

リセットには以下の3種類がある。

・システムリセット

・パワーリセット

・バックアップドメインリセット

システムリセット

システムリセットでは前回の記事(STM32F7 PWR(電源管理))でも出てきたRTC関連のレジスタとバックアップSRAM以外のレジスタが初期値にリセットされる。

システムリセットは以下のいずれかの条件で発生する。

・NRSTピンがLレベルになる

・WWDGのカウント値が0x3F以下になる

・IWDGのカウント値が0x00になる

・ソフトウェアリセットが発生する

・nRST_STDBYビットがクリアされた状態でスタンバイモードに入る

・nRST_STOPビットがクリアされた状態でストップモードに入る

※ソフトウェアリセットはST社のペリフェラルの方ではなく、Cortexコアの方にあるAIRCRレジスタのSYSRESETREQビットをセットすると発生する。

※nRST_STDBYビット、nRST_STOPビットは共にオプションバイトにある。

パワーリセット

パワーリセットもシステムリセットと同じくRTC関連のレジスタとバックアップSRAM以外のレジスタが初期値にリセットされる。

パワーリセットは以下のいずれかの条件で発生する。

・VDDピンの電圧が設定したブラウンアウトレベルを跨ぐ

・VDDピンの電圧がPOR/PDR閾値を跨ぐ

・STANDBYモードから抜ける

※ブラウンアウトレベルやPOR/PDR閾値については(STM32F7 PWR(電源管理))に書かれている。

バックアップドメインリセット

バックアップドメインリセットではRTC関連のレジスタが初期値にリセットされる。

バックアップドメインリセットは以下のいずれかの条件で発生する。

・RCC_BDCRレジスタのBDRSTビットをセット

・完全な電源OFF状態からのVdd端子、またはVbat端子の電圧の立ち上がり

リセットについての補足

電源の状態と発生するリセット

マイコンの電源が切れたときのパワーリセットとバックアップドメインリセットの違いが分かりにくかったので表にまとめた。

| 電源の状態 | 発生するリセット |

| VDD遮断 | パワーリセット |

| VBAT遮断 | バックアップドメインリセット |

| VDD/VBAT遮断 | パワーリセット + バックアップドメインリセット |

バックアップSRAMの初期化について

上の3つのリセットのいずれでもバックアップSRAMが初期化されるとはどこにも書かれていない。しかしSRAMの内容はVDD/VBATが供給されていれば保持されるとも書かれているので、これが遮断されれば内容は失われるはずである。

これは個人的な予想だが、VDD/VBATが遮断されればSRAMの内容は失われるものの、いかなるリセットが発生してもバックアップSRAMの0xFFなどへの初期化は行われないということだと思う。つまりSRAMの初期化はソフトウェアで行う必要がある。

クロック

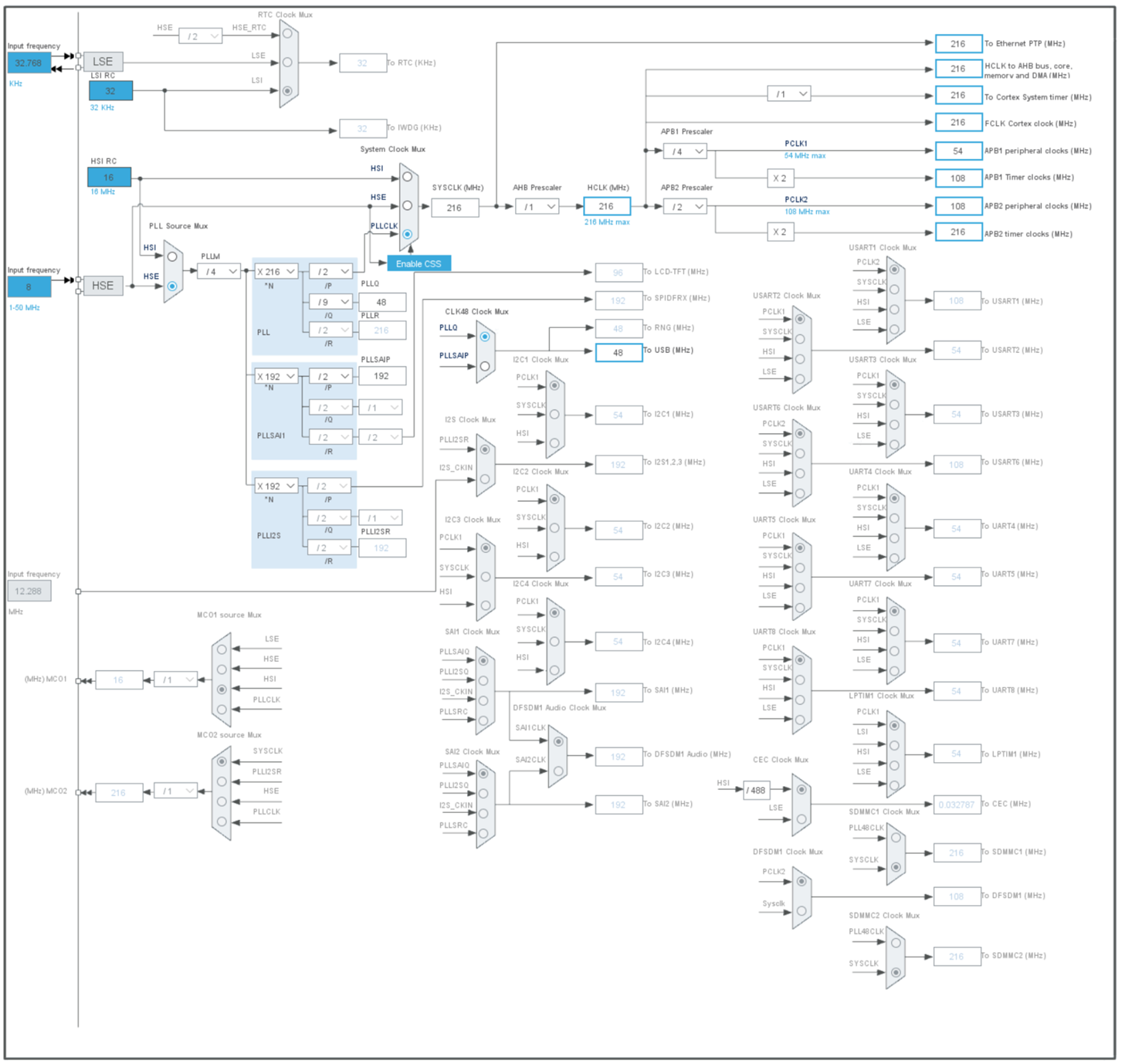

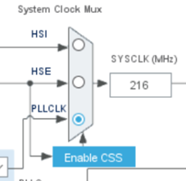

クロックについてはまずはSTM32CubeMXでクロックの設定を行う際に出てくるブロック図を見るのが一番わかりやすいだろう。

クロック源

STM32F7のシステムクロックとして以下の3つのクロック源から選択できる。

・高速内蔵クロック(HSI)

・高速外部クロック(HSE)

・PLL

なお、マイコンの起動直後(リセット直後)の設定ではマイコンは16MHzのHSIで動作している。

他にも下記の2つのクロック源が用意されているが、これはRTCやIWDGに使われることを目的としている。これらの詳細についてはマニュアルP158に書かれている。

・低速内蔵クロック(LSI)

・低速外部クロック(LSE)

ペリフェラルのクロック

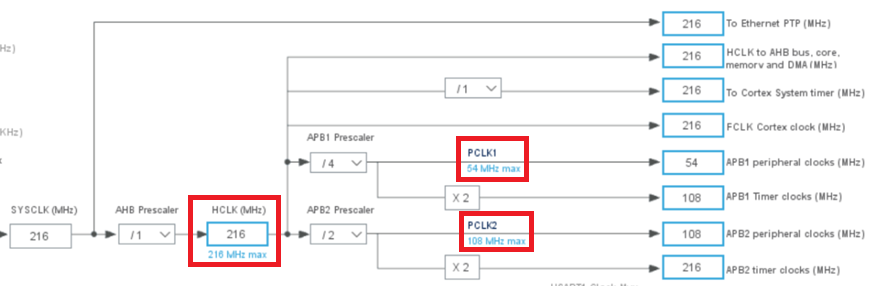

ペリフェラルへはHCLK、PCLK1、PCLK2のいずれかからクロックが供給される。

ADCやUARTなど、各ペリフェラルには個別にクロックを供給でき、クロックが供給されていないペリフェラルのレジスタに対する書き込み、読み込みアクセスはできない。

ペリフェラルのクロックを有効にしてから実際にペリフェラルのレジスタにアクセスするまでの間にPCLK1、またはPCLK2、またはHCLKの2クロック分待たないといけない。

各ペリフェラルに対するクロック供給の設定はRCC_AHCxENRレジスタ、またはTCC_APBxENRyレジスタで行う。

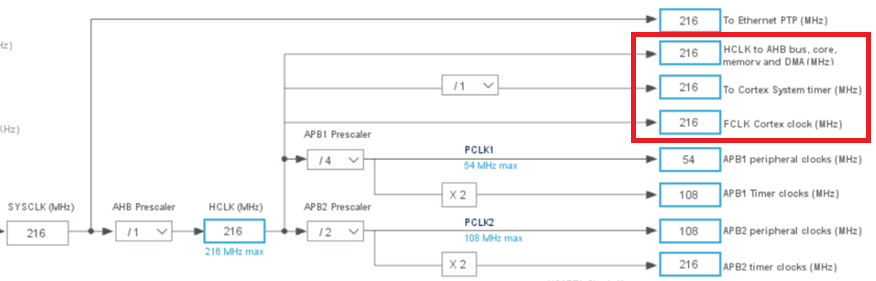

Cortexコアのクロック

CortexコアにはHCLKとFCLKが供給されており、主にHCLKがCortexのコアを動かしている。

FCLKはCortexのフリーランニングクロック(Free Running Clock)として使われており、デバッグや割込みの読み込みに使われている。基本的にHCLKと同クロックで同期しているが、スリープモードなどの省電力モードになるとHCLKが停止するのに対してFCLKは停止しない。つまり省電力モード時でもデバッグや割込みのトレースを可能としている。

Cortexコア内に存在するSysTickにはHCLK、またはそれを8分周したクロックが供給される。どのクロックを使うかはCortexコアののSYST_CSRレジスタのCLKSOURCEビットで設定する

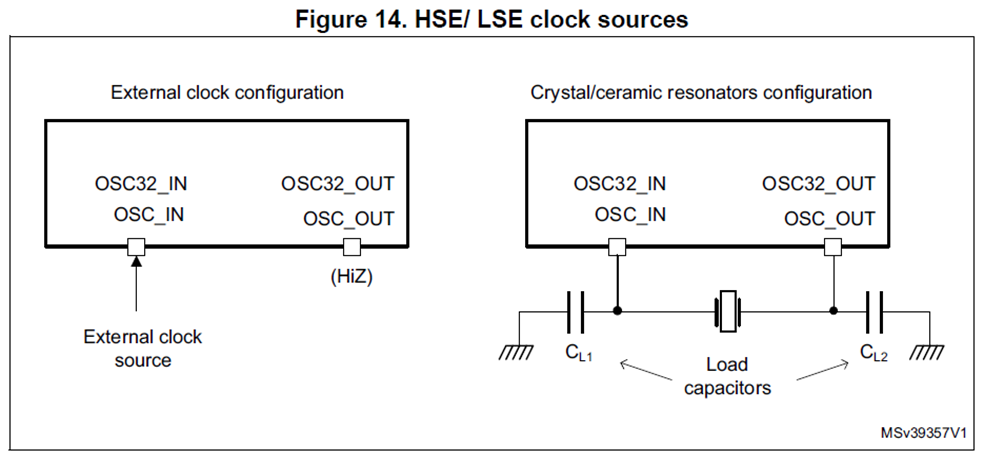

HSEクロックについて

HSEクロックはOSC_INピンとOSC_OUTピンに水晶発振子を接続するかOSC_INピンに外部クロックを供給することで使用可能になる。

マイコン起動後、RCC_CRレジスタのHSERDYビットがハードウェアによってセットされるまでHSEは使えない。

HSIクロックについて

HSIクロックは内蔵された16MHzのRC発振器によって生成される。マイコン起動後に使用可能になるまでの時間がHSEよりも短いが、精度が悪い。

工場にて25℃時に1%以下の精度となるように調整されている。それでも足りない場合はRCC_CRレジスタのHSITRIMビットでHSIクロックの調整が可能。

マイコン起動後、RCC_CRレジスタのHSIRDYビットがハードウェアによってセットされるまでHSIは使えない。

CSSという機能を使ってHSEに異常があった場合のバックアップとしてHSIを使うことができる。

PLLについて

PLLはHSEかHSIを入力としてCortexやペリフェラルに使う216MHzまでの高速クロックと、USBやRNG用の48MHzのクロックの2つを出力する。

PLLは一度有効化されると設定を変更することができないため、入力やプリスケーラ値やPLL倍数などは有効にする前に設定しておかなければならない。

CSSについての詳細

HSEをクロック源、またはHSEをPLLへの入力として使用している場合、CSS(Colock Security System)を有効にしているとHSEに異常が発生した場合に割込みが発生し、タイマー1とタイマー8にブレークイベントを送り、マイコンのクロック源はHSIに切り替わる。ただし、同時にPLLも全て無効になるためUSB用のクロックなども停止してしまう。

CSSによって発生する割込みはノンマスカブル割込み(NMI)なので割込みを止めたい場合はRCC_CIRレジスタのCSSCビットをセットすることによって割込みフラグをクリアする必要がある。

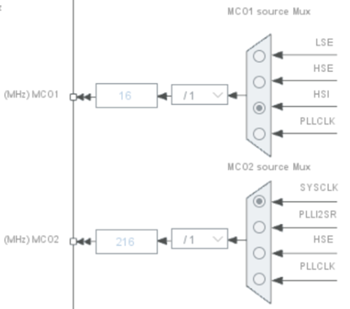

クロック出力

RCC_CFGRレジスタのMCO1PREビットとMCO1ビットを設定することでMCO1ピン(PA8ピン)から以下のクロックを出力することができる。

・HSI

・HSE

・PLL

・LSE

RCC_CFGRレジスタのMCO2PREビットとMCO2ビットを設定することでMCO2ピン(PC9ピン)から以下のクロックを出力することができる。

・HSE

・SYSCLK

・PLL

・PLLI2S

このとき、MCO1、MCO2ともにクロックの出力に使用する場合はピンの設定を兼用モードにすること。

クロック周波数の測定

マニュアルのP160からP162まで内蔵、または外付けクロックの周波数を測定する方法が書かれているがここれは省略する。

実際に試したわけではないがあまり正確に測れるものではなく、大雑把な測定にとどまるようだ。

-

前の記事

STM32F7 PWR(電源管理) 2020.07.12

-

次の記事

STM32F7 FLASH(フラッシュメモリ) 2020.09.27